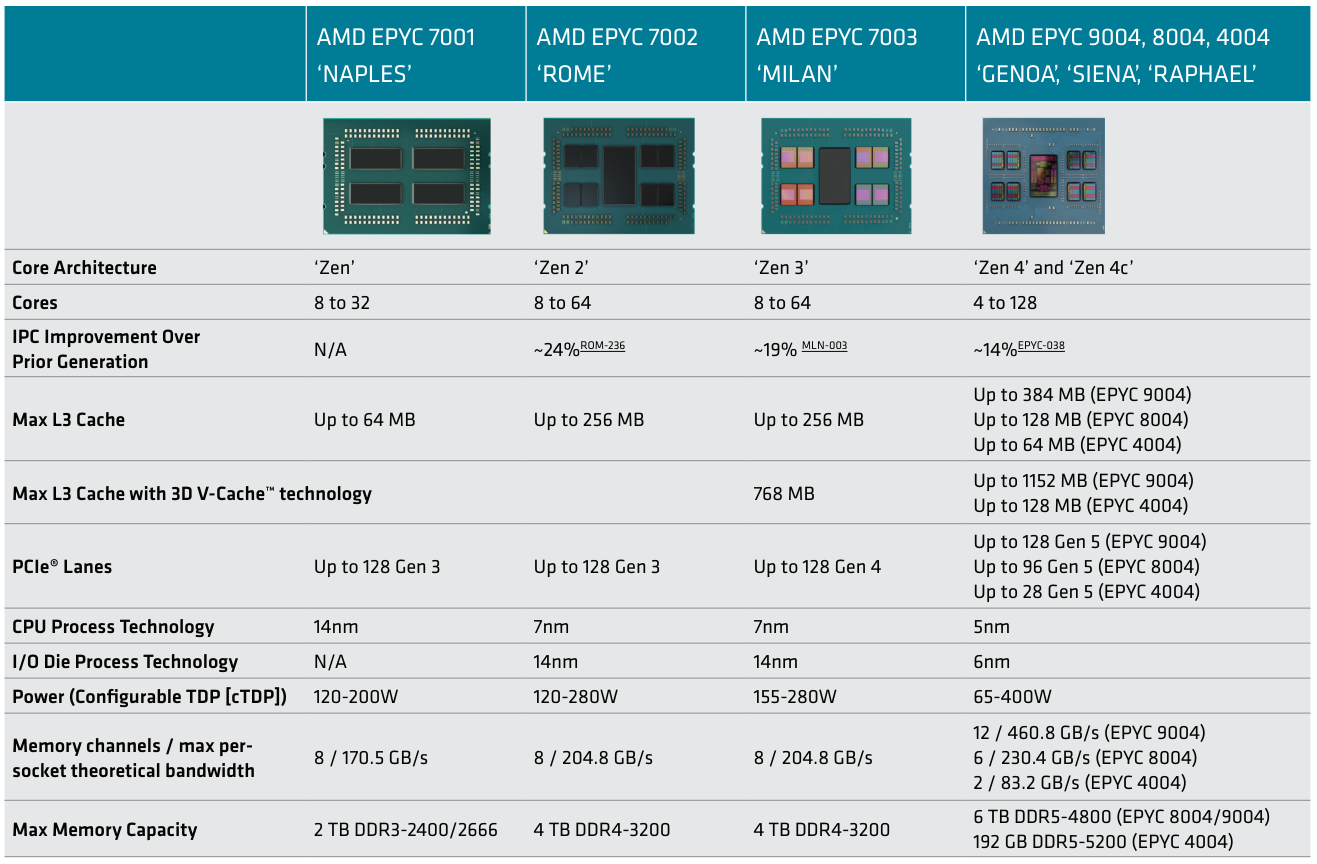

一、AMD EPYC Family Overview

| Processor name | Microarchitecture | Socket | Family / Model | source |

|---|---|---|---|---|

| AMD EPYC 7001 Naples | Zen | SP3 | AMD Family 17h Models 00h-0Fh | AMD Revision Guide for AMD Family 17h Models 00h-0Fh |

| AMD EPYC 7002 Rome | Zen 2 | SP3 | AMD Family 17h Models 30h-3Fh | AMD Revision Guide for AMD Family 17h Models 30h-3Fh |

| AMD EPYC 7003 Milan | Zen 3 | SP3 | AMD Family 19h Models 00h-0Fh | AMD Revision Guide for AMD Family 19h Models 00h-0Fh |

| AMD EPYC 9004 Genoa and Bergamo | Zen 4 and Zen 4c | SP5 | AMD Family 19h Models 10h-1Fh | AMD Revision Guide for AMD Family 19h Models 10h-1Fh |

| AMD EPYC 8004 Siena | Zen 4c | SP6 | AMD Family 19h Models A0h–AFh | — |

二、Rome Processors

1、Single socket CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 4 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 7232P | 8 | 16 | 3.1 | 3.2 | 120 | 4 | 32 | 2 x CCD 1 x I/OD | 4 x 2 | 8 | 3200 | 85.3 | 128 |

| 7302P | 16 | 32 | 3 | 3.3 | 155 | 8 | 128 | 4 x CCD 1 x I/OD | 8 x 2 | 8 | 3200 | 204.8 | 128 |

| 7402P | 24 | 48 | 2.8 | 3.35 | 180 | 12 | 128 | 4 x CCD 1 x I/OD | 8 x 3 | 8 | 3200 | 204.8 | 128 |

| 7502P | 32 | 64 | 2.5 | 3.35 | 180 | 16 | 128 | 4 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 7702P | 64 | 128 | 2 | 3.35 | 200 | 32 | 256 | 8 x CCD 1 x I/OD | 16 x 4 | 8 | 3200 | 204.8 | 128 |

2、Dual socket CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 4 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 7252 | 8 | 16 | 3.1 | 3.2 | 120 | 4 | 64 | 2 x CCD 1 x I/OD | 4 x 2 | 8 | 3200 | 85.3 | 128 |

| 7262 | 8 | 16 | 3.2 | 3.4 | 155 | 4 | 128 | 4 x CCD 1 x I/OD | 8 x 1 | 8 | 3200 | 204.8 | 128 |

| 7272 | 12 | 24 | 2.9 | 3.2 | 120 | 6 | 64 | 2 x CCD 1 x I/OD | 4 x 3 | 8 | 3200 | 85.3 | 128 |

| 7282 | 16 | 32 | 2.8 | 3.2 | 120 | 8 | 64 | 2 x CCD 1 x I/OD | 4 x 4 | 8 | 3200 | 85.3 | 128 |

| 7302 | 16 | 32 | 3 | 3.3 | 155 | 8 | 128 | 4 x CCD 1 x I/OD | 8 x 2 | 8 | 3200 | 204.8 | 128 |

| 7352 | 24 | 48 | 2.3 | 3.2 | 155 | 12 | 128 | 4 x CCD 1 x I/OD | 8 x 3 | 8 | 3200 | 204.8 | 128 |

| 7402 | 24 | 48 | 2.8 | 3.35 | 180 | 12 | 128 | 4 x CCD 1 x I/OD | 8 x 3 | 8 | 3200 | 204.8 | 128 |

| 7452 | 32 | 64 | 2.35 | 3.35 | 155 | 16 | 128 | 4 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 7502 | 32 | 64 | 2.5 | 3.35 | 180 | 16 | 128 | 4 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 7532 | 32 | 64 | 2.4 | 3.3 | 200 | 16 | 256 | 8 x CCD 1 x I/OD | 16 x 2 | 8 | 3200 | 204.8 | 128 |

| 7542 | 32 | 64 | 2.9 | 3.4 | 225 | 16 | 128 | 4 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 7552 | 48 | 96 | 2.2 | 3.35 | 200 | 24 | 192 | 6 x CCD 1 x I/OD | 12 x 4 | 8 | 3200 | 204.8 | 128 |

| 7642 | 48 | 96 | 2.3 | 3.3 | 225 | 24 | 256 | 8 x CCD 1 x I/OD | 16 x 3 | 8 | 3200 | 204.8 | 128 |

| 7662 | 64 | 128 | 2 | 3.3 | 225 | 32 | 256 | 8 x CCD 1 x I/OD | 16 x 4 | 8 | 3200 | 204.8 | 128 |

| 7702 | 64 | 128 | 2 | 3.35 | 200 | 32 | 256 | 8 x CCD 1 x I/OD | 16 x 4 | 8 | 3200 | 204.8 | 128 |

| 7742 | 64 | 128 | 2.25 | 3.4 | 225 | 32 | 256 | 8 x CCD 1 x I/OD | 16 x 4 | 8 | 3200 | 204.8 | 128 |

| 7F32 | 8 | 16 | 3.7 | 3.9 | 180 | 4 | 128 | 4 x CCD 1 x I/OD | 8 x 1 | 8 | 3200 | 204.8 | 128 |

| 7F52 | 16 | 32 | 3.5 | 3.9 | 240 | 8 | 256 | 8 x CCD 1 x I/OD | 16 x 1 | 8 | 3200 | 204.8 | 128 |

| 7F72 | 24 | 48 | 3.2 | 3.7 | 240 | 12 | 192 | 6 x CCD 1 x I/OD | 12 x 2 | 8 | 3200 | 204.8 | 128 |

| 7H12 | 64 | 128 | 2.6 | 3.3 | 280 | 32 | 256 | 8 x CCD 1 x I/OD | 16 x 4 | 8 | 3200 | 204.8 | 128 |

- 7H12 : HPC-optimized Processor

- 7F32 / 7F52 /7F72 : Frequency-optimized Processors

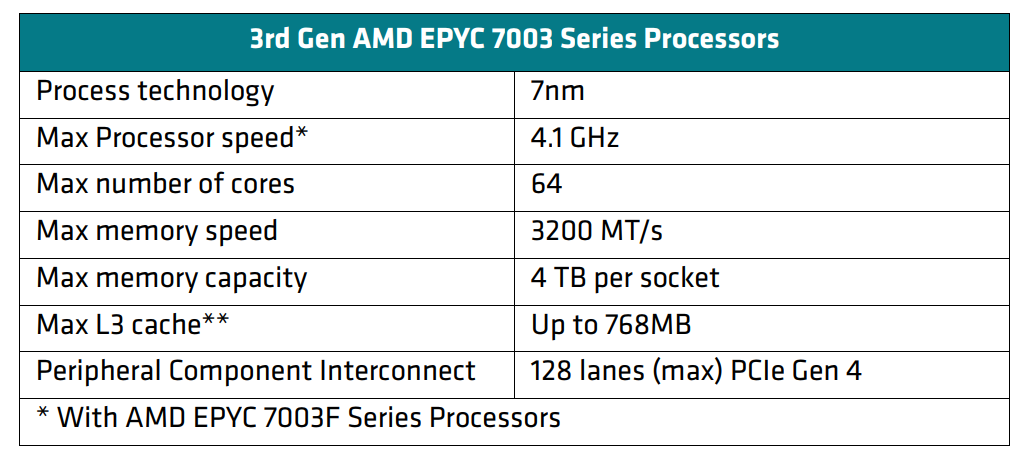

三、Milan Processors

AMD EPYC 7003系列处理器基于“Zen 3”计算核心。“Zen 3”核心采用7纳米工艺制造,旨在提供比之前一代“Zen”核心更高的每周期指令(IPC)效能。每个核心包括经过优化的32 KB 8路L1 I缓存和32 KB 8路L1 D缓存,以及一个私有的512 KB 统一(指令/数据)L2缓存。所有缓存使用64字节的缓存行大小。

1、Processor Identification

- Family: 19h (identifies the “Zen 3” architecture)

- Model: 00-01h (identifies the Server Program)

- Stepping: May be used to further identify minor design changes

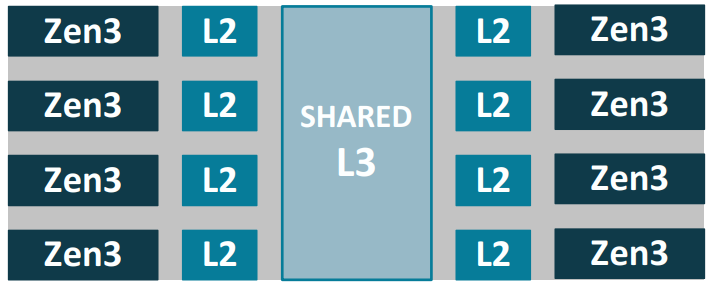

2、Core Complex (CCX) and Core Complex Die (CCD)

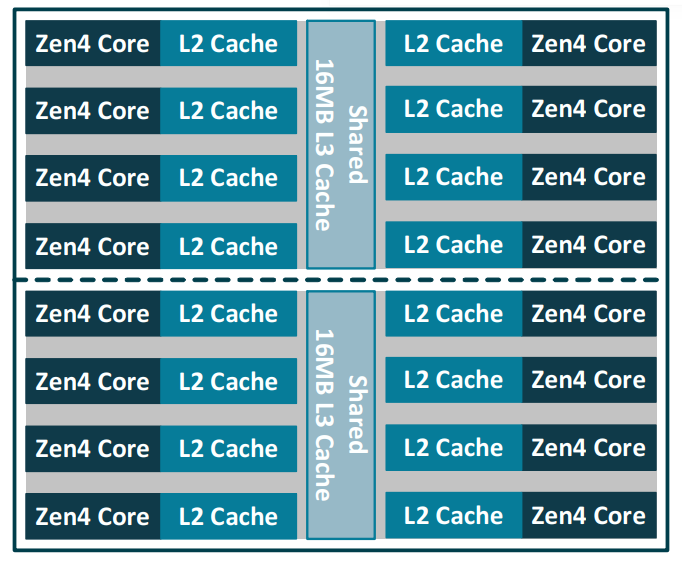

以下图片展示了高达八个“Zen 3”核心计算单元如何共享一个L3或最后一级缓存(LLC)。这种分组称为核心复合体(CCX)。在每个核心上启用同时多线程(SMT)可以使单个CCX支持高达16个并发硬件线程,高达4MB的L2缓存和32MB的基本L3缓存(或者在具有3D V-Cache的AMD EPYC 7003 OPNs上可达96MB L3)。AMD EPYC 7003系列处理器在单个核心复合体芯片(CCD)内包含一个单一的CCX。

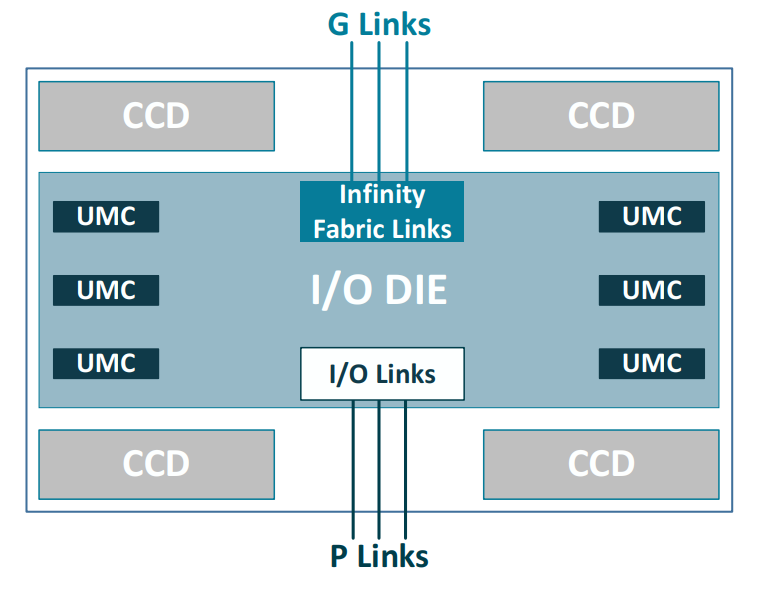

3、I/O Die (Infinity Fabric™)

CCD通过I/O芯片(IOD)连接到内存、I/O和彼此。每个CCD通过专用的高速全局内存互连(GMI)链路连接到IOD。IOD还包含内存通道、PCIe® Gen4通道和Infinity Fabric链路。所有芯片(或芯片组)通过AMD的Infinity Fabric技术相互连接。现在,Fabric时(FCLK)可以运行高达1600MHz,并且可以与运行在1600MHz(MEMCLK)的DDR4-3200内存DIMM配对,进一步改善内存延迟。

4、Memory and I/O

第三代AMD EPYC处理器为内存子系统带来了额外的性能能力和新的6路交错模式。每个AMD EPYC 7003系列处理器都有8个通用内存控制器(UMC)。每个UMC(或内存通道)可以支持每通道2个DIMM(DPC),每个插槽最多支持16个DIMM。第三代AMD EPYC处理器可以支持4TB的DDR4内存。IOD具有支持4、6和8个内存通道配置的灵活性。8个内存通道是最常见的,通常提供最佳性能。每个处理器有8个x16位I/O链路,为单插槽平台的PCIe子系统提供高达128条高速PCIe Gen4 I/O通道,双插槽平台则提供高达160条通道。

5、NUMA Topology

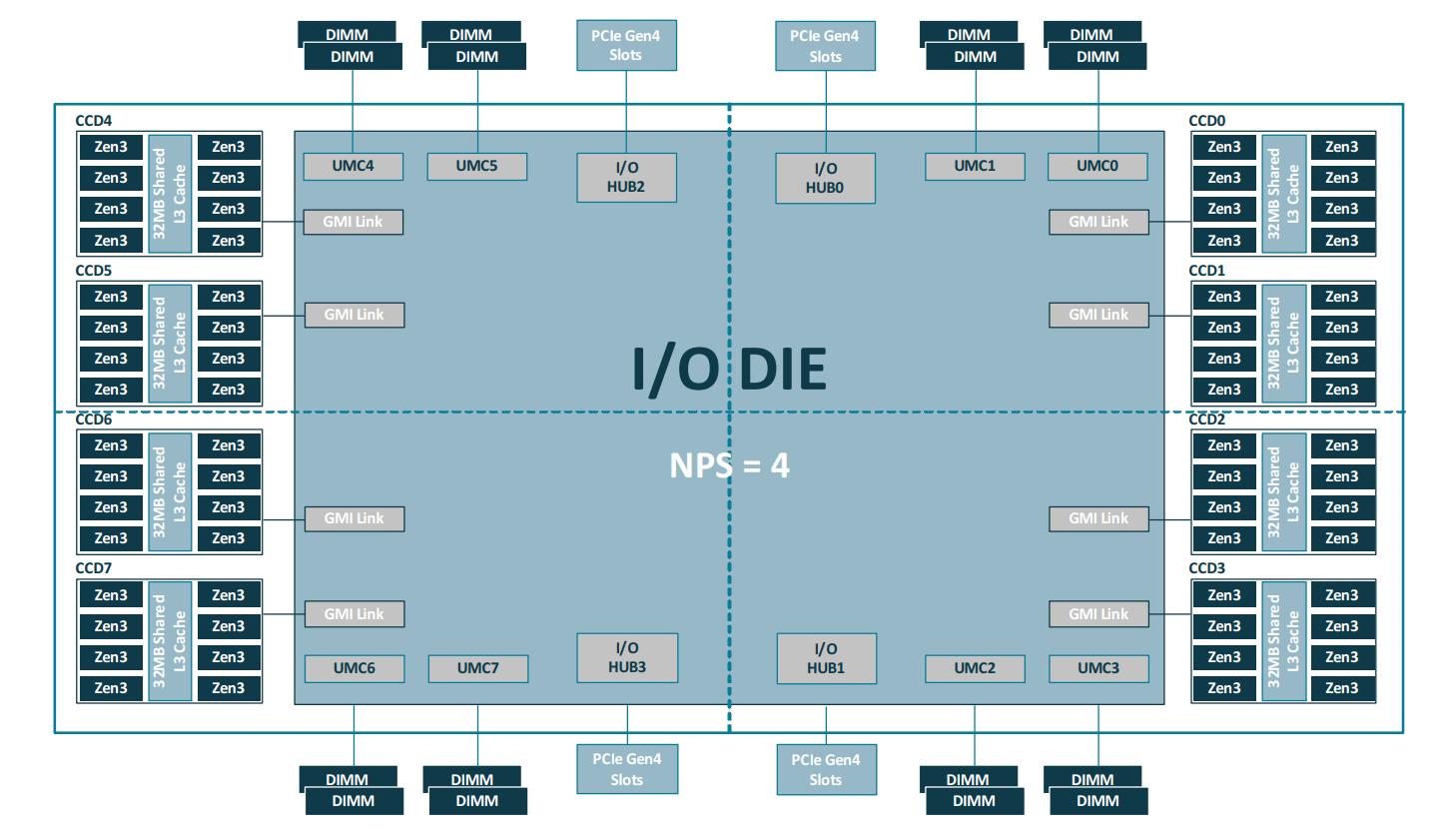

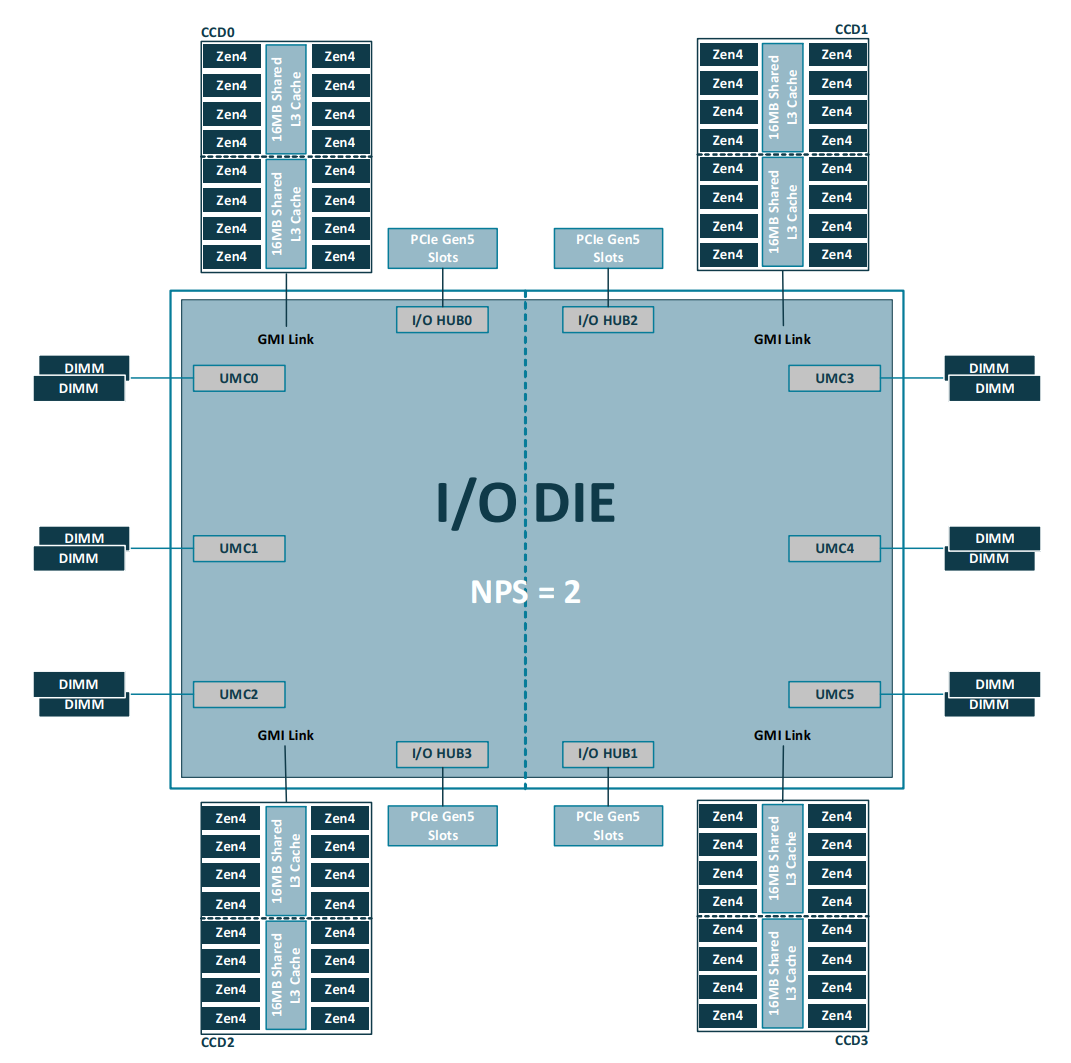

AMD EPYC 7003系列处理器采用非均匀内存访问(NUMA)微体系结构。此外,用户可以使用系统BIOS设置优化这种NUMA拓扑以适应其特定的操作环境和工作负载。通过使用NUMA节点每个插槽(NPS)BIOS设置,系统可以设置不同的NUMA配置。例如,如果我们设置NPS=4,就像上图中所示,我们可以将处理器划分为四个象限。每个象限将包含2个CCD、2个UMC和1个I/O Hub,就像上图中所示。最接近处理器内存-I/O距离的是在同一象限内的核心、内存控制器和I/O之间。最远的距离是在对角象限中一个核心和内存控制器或IO集线器之间。在基于NUMA的系统中,核心、内存和IO的位置是调整性能的重要方面。

此外,NPS设置还控制内存控制器的交错模式。对于每个NUMA节点,该节点内的所有通道都是交错的。设置NPS=4将处理器划分为四个NUMA域。处理器的每个逻辑象限都配置为自己的NUMA域。内存在每个象限中的两个内存通道之间交错。PCIe设备将位于处理器上四个NUMA域中的一个,具体取决于具有该设备PCIe根的IO芯片的象限。

与此同时,NPS=1表示每个插槽一个NUMA节点。此设置将处理器上的所有内存通道配置为单个NUMA域,即处理器上的所有核心、所有连接的内存和所有连接到SoC的PCIe设备都在一个NUMA域中。内存访问将交错在所有八个内存通道中,形成一个单一的地址空间。

随着NPS设置变得更加精细,交错的通道数量相应减少。设置NPS=2将每个插槽划分为2个NUMA域,即在相同的4个CCD NUMA域内交错相应的四个内存通道。每个SoC的一半核心和一半内存通道被分组到一个NUMA域中,剩余的核心和内存通道被分组到第二个域中。内存在每个NUMA域的四个内存通道之间交错。

此外,某些环境的性能可能通过将工作负载与共享单个LLC的计算核心关联来进一步改善。LLC(最后一级缓存,或L3缓存)作为NUMA BIOS设置暴露了这种能力。启用此设置将每个CCD等同于一个单独的NUMA域,每个CCD有一个唯一的L3缓存。一个具有8个CCD的单个7003处理器将有8个NUMA节点。总之,单个EPYC 7003系列处理器可以支持从单个NUMA节点系统,一直到每个插槽多达8个NUMA节点的配置。

6、Dual-Socket Configurations

AMD EPYC 7003系列处理器支持单插槽或双插槽系统配置。名称中带有‘P’后缀的处理器设计用于单插槽配置。在双插槽配置中,两个处理器必须完全相同。不能在同一个双插槽系统中使用两个不同的处理器OPN或steppings。

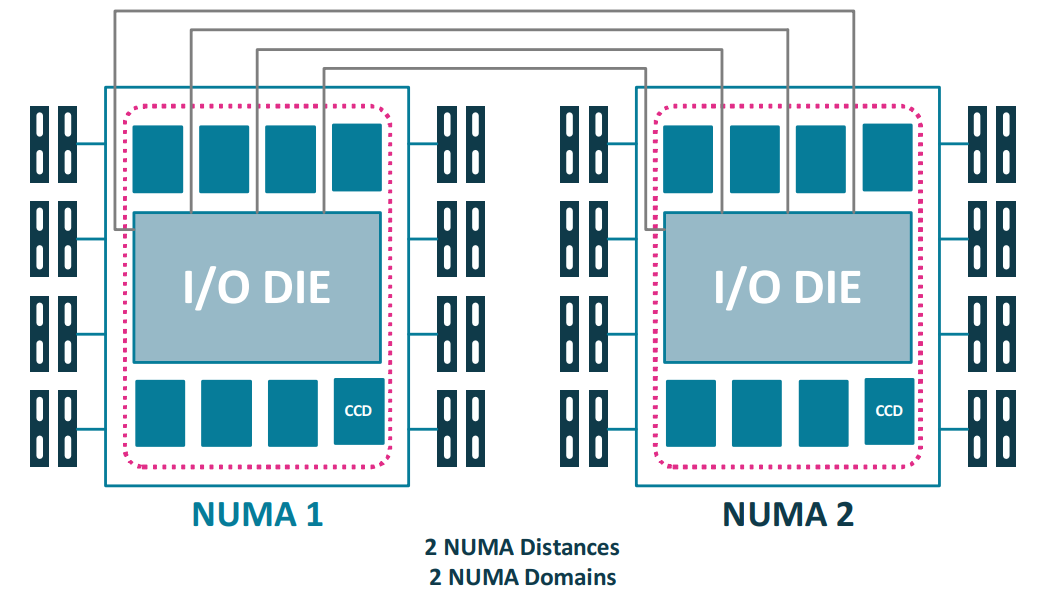

在双插槽系统中,两个相同的EPYC 7003系列SoC通过它们对应的Infinity Fabric或外部全局内存互连(xGMI)链路连接。这样就在两个处理器之间创建了高带宽、低延迟的互连。系统制造商可以根据I/O和带宽系统设计目标使用3或4个Infinity Fabric链接。Infinity Fabric链接利用与系统上的PCIe通道相同的物理连接。每个链接最多使用16条PCIe通道。在典型的双插槽系统中,每个插槽的64条PCIe通道(4个链接)将被重新配置为Infinity Fabric连接,因此每个插槽仍然有64条剩余的PCIe通道,系统总共仍然有128条PCIe通道。在某些情况下,系统设计师可能希望为系统暴露更多的PCIe通道,通过将Infinity Fabric链接的数量从4减少到3。在这些情况下,系统设计师可以为PCIe分配多达160条通道(每个插槽80条),每个插槽只使用48条PCIe通道进行Infinity Fabric链接,而不是64条。双插槽系统总共有16个内存通道,每个插槽有8个。双插槽系统可以以多种方式配置,包括1、2、4、8或16个NUMA域。

7、Single socket CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 4 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 7313P | 16 | 32 | 3 | 3.7 | 155 | 8 | 128 | 4 x CCD 1 x I/OD | 4 x 4 | 8 | 3200 | 204.8 | 128 |

| 7443P | 24 | 48 | 2.85 | 4 | 200 | 12 | 128 | 4 x CCD 1 x I/OD | 4 x 6 | 8 | 3200 | 204.8 | 128 |

| 7543P | 32 | 64 | 2.8 | 3.7 | 225 | 16 | 256 | 8 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 7713P | 64 | 128 | 2 | 3.675 | 225 | 32 | 256 | 8 x CCD 1 x I/OD | 8 x 8 | 8 | 3200 | 204.8 | 128 |

8、Dual socket CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 4 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 72F3 | 8 | 16 | 3.7 | 4.1 | 180 | 4 | 256 | 8 x CCD 1 x I/OD | 8 x 1 | 8 | 3200 | 204.8 | 128 |

| 7313 | 16 | 32 | 3 | 3.7 | 155 | 8 | 128 | 4 x CCD 1 x I/OD | 4 x 4 | 8 | 3200 | 204.8 | 128 |

| 7343 | 16 | 32 | 3.2 | 3.9 | 190 | 8 | 128 | 4 x CCD 1 x I/OD | 4 x 4 | 8 | 3200 | 204.8 | 128 |

| 73F3 | 16 | 32 | 3.5 | 4 | 240 | 8 | 256 | 8 x CCD 1 x I/OD | 8 x 2 | 8 | 3200 | 204.8 | 128 |

| 7413 | 24 | 48 | 2.65 | 3.6 | 180 | 12 | 128 | 4 x CCD 1 x I/OD | 4 x 6 | 8 | 3200 | 204.8 | 128 |

| 7443 | 24 | 48 | 2.85 | 4 | 200 | 12 | 128 | 4 x CCD 1 x I/OD | 4 x 6 | 8 | 3200 | 204.8 | 128 |

| 7453 | 28 | 56 | 2.75 | 3.45 | 225 | 14 | 64 | 4 x CCD 1 x I/OD | 4 x 7 | 8 | 3200 | 204.8 | 128 |

| 74F3 | 24 | 48 | 3.2 | 4 | 240 | 12 | 256 | 8 x CCD 1 x I/OD | 8 x 3 | 8 | 3200 | 204.8 | 128 |

| 7513 | 32 | 64 | 2.6 | 3.65 | 200 | 16 | 128 | 8 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 7543 | 32 | 64 | 2.8 | 3.7 | 225 | 16 | 256 | 8 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 75F3 | 32 | 64 | 2.95 | 4 | 280 | 16 | 256 | 8 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 7643 | 48 | 96 | 2.3 | 3.6 | 225 | 24 | 256 | 8 x CCD 1 x I/OD | 8 x 6 | 8 | 3200 | 204.8 | 128 |

| 7663 | 56 | 112 | 2 | 3.5 | 240 | 28 | 256 | 8 x CCD 1 x I/OD | 8 x 7 | 8 | 3200 | 204.8 | 128 |

| 7713 | 64 | 128 | 2 | 3.675 | 225 | 32 | 256 | 8 x CCD 1 x I/OD | 8 x 8 | 8 | 3200 | 204.8 | 128 |

| 7763 | 64 | 128 | 2.45 | 3.5 | 280 | 32 | 256 | 8 x CCD 1 x I/OD | 8 x 8 | 8 | 3200 | 204.8 | 128 |

- 72F3 / 73F3 / 74F3 / 75F3 : High-Frequency Processors.

9、3D V-CACHE CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 4 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 7373X | 16 | 32 | 3.05 | 3.8 | 240 | 8 | 768 | 8 x CCD 1 x I/OD | 8 x 2 | 8 | 3200 | 204.8 | 128 |

| 7473X | 24 | 48 | 2.8 | 3.7 | 240 | 12 | 768 | 8 x CCD 1 x I/OD | 8 x 3 | 8 | 3200 | 204.8 | 128 |

| 7573X | 32 | 64 | 2.8 | 3.6 | 280 | 16 | 768 | 8 x CCD 1 x I/OD | 8 x 4 | 8 | 3200 | 204.8 | 128 |

| 7773X | 64 | 128 | 2.2 | 3.5 | 280 | 33 | 768 | 8 x CCD 1 x I/OD | 8 x 8 | 8 | 3200 | 204.8 | 128 |

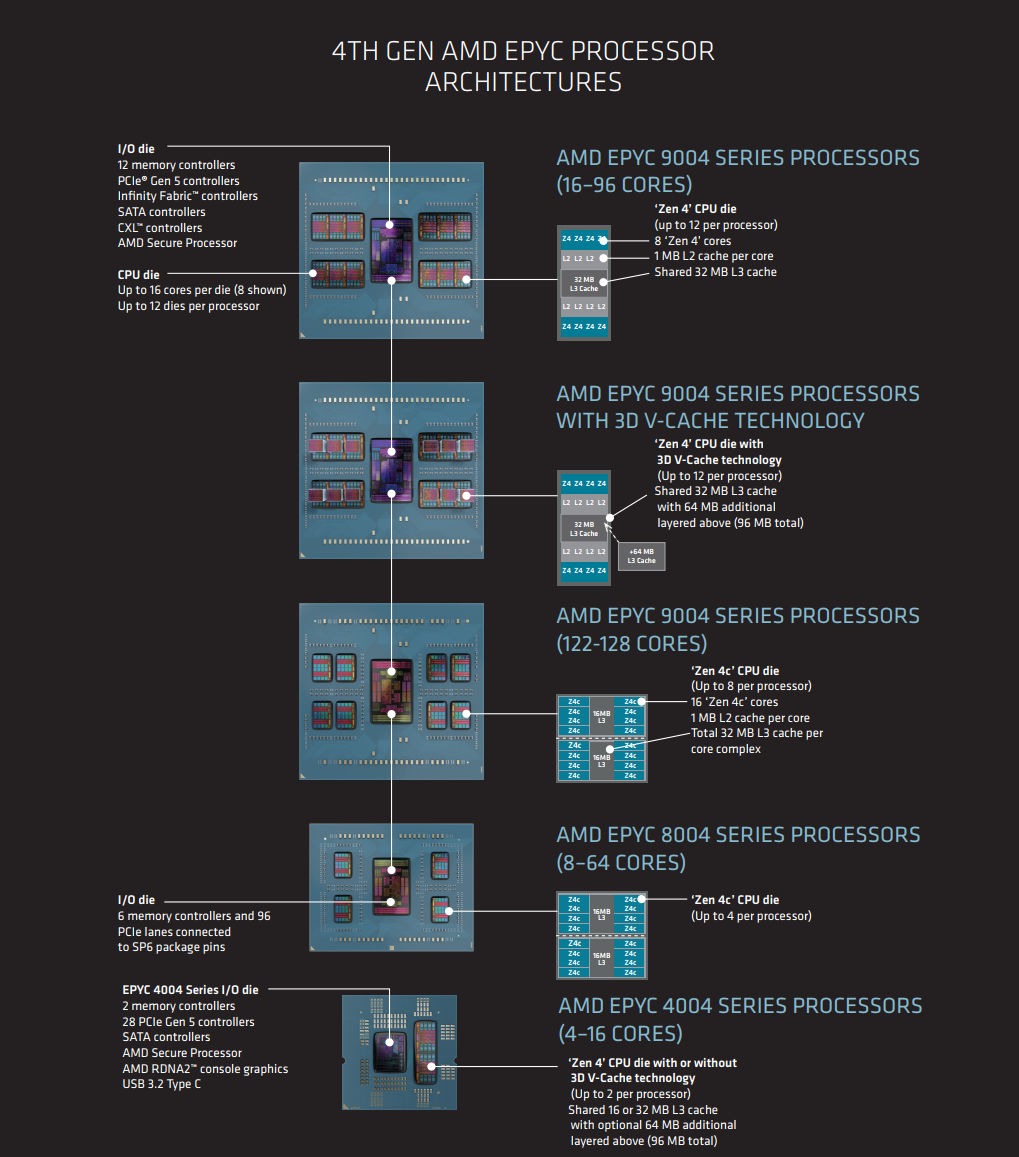

四、Genoa and Bergamo Processors

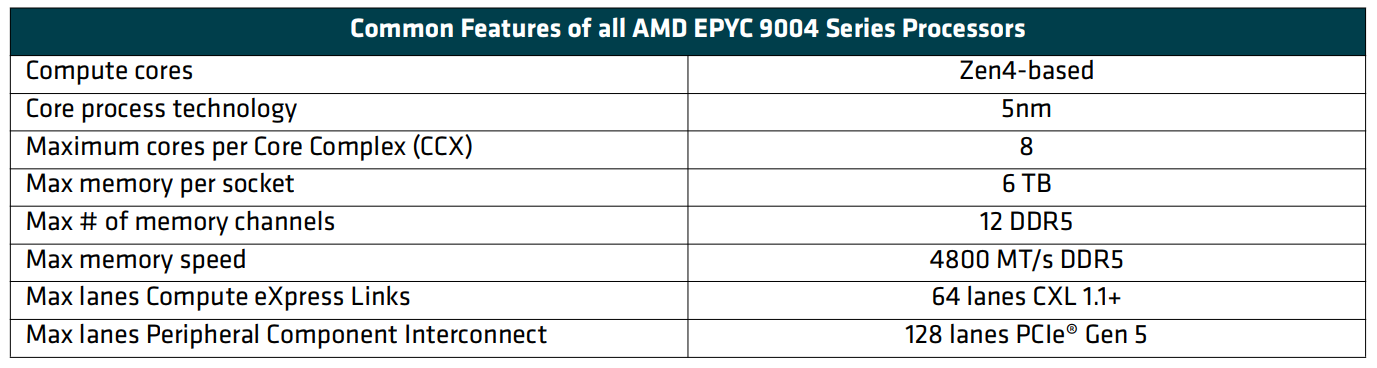

1、General Specifications

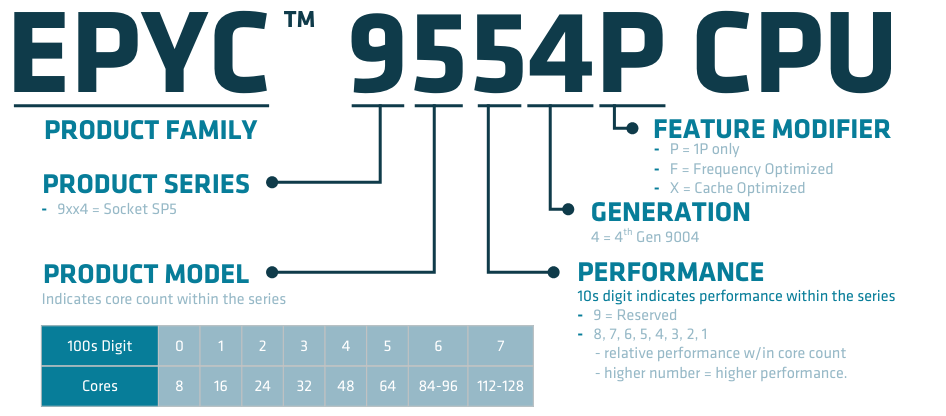

AMD EPYC™ 9004系列处理器代表了AMD EPYC服务器级处理器的第四代。这一代的AMD EPYC处理器采用了AMD最新的基于“Zen 4”的计算核心,下一代Infinity Fabric,下一代内存和I/O技术,并使用了新的SP5插座/封装。AMD EPYC 9004系列处理器提供多种配置,包括不同数量的核心、热设计功耗(TDP)、频率、缓存大小等,这些配置与AMD现有的服务器产品组合相辅相成,进一步提升了性能、功耗效率和价值。下表列出了所有AMD EPYC 9004系列处理器共同具有的特性。

2、Model-Specific Features

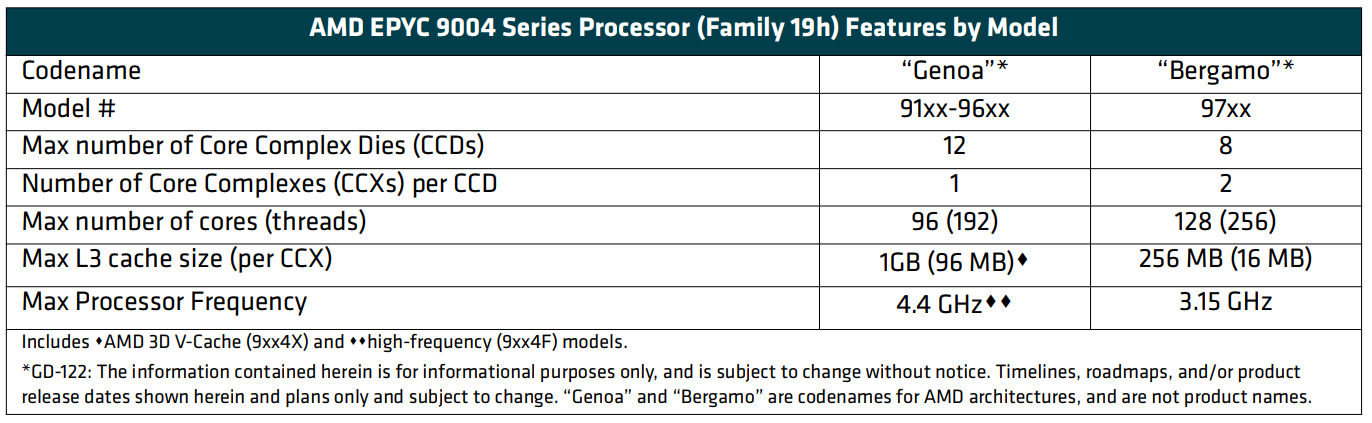

如下表所示,不同型号的第四代AMD EPYC处理器具有不同的功能集。

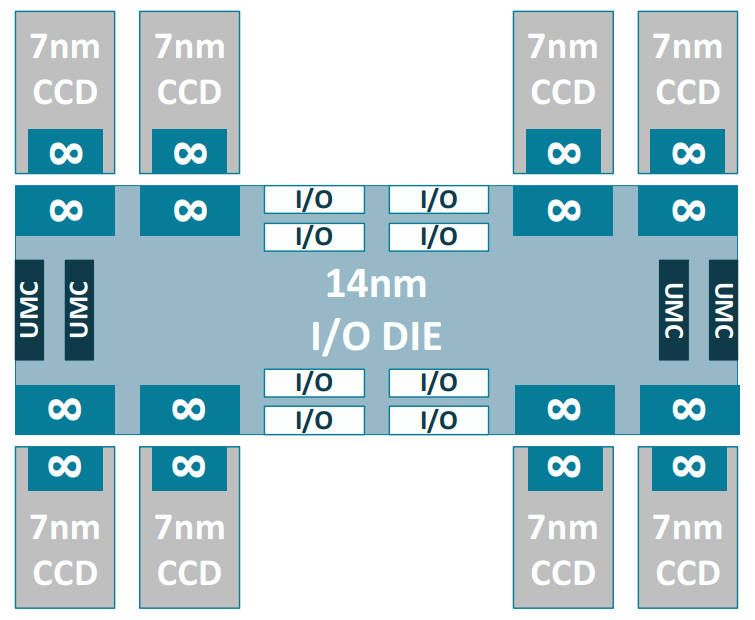

3、Processor Layout

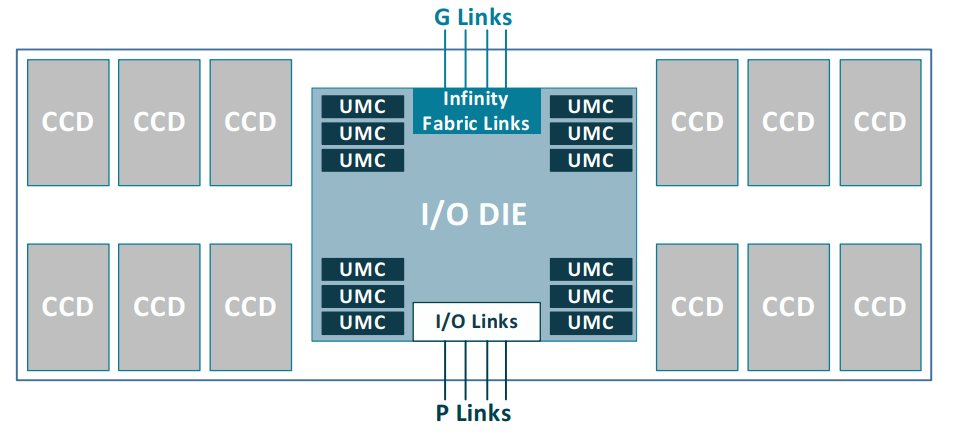

AMD EPYC 9004系列处理器将计算核心、内存控制器、I/O控制器、RAS(可靠性、可用性和可维护性)以及安全功能整合到一个集成的系统芯片(SoC)中。AMD EPYC 9004系列处理器保留了先前成功的AMD EPYC处理器的多芯片模块(MCM)芯片组架构,并进一步改进了SoC组件。SoC包括核心复合体芯片(CCD),其中包含核心复合体(CCX),其中包含基于“Zen 4”的核心。CCD环绕着中央高速I/O芯片(并通过Infinity Fabric互连)。接下来的部分描述了这些组件中的每一个。

4、“Zen 4” Core

AMD EPYC 9004系列处理器基于“Zen 4”计算核心。“Zen 4”核心采用5纳米工艺制造,旨在提供比先前一代“Zen”核心更高的每周期指令(IPC)效能和频率改进。每个核心的L2缓存比前一代更大,并且缓存效率得到了提高。“Zen 4”核心包括以下内容:

- 高达32 KB的8路L1 I缓存和32 KB的8路L1 D缓存

- 高达1MB的私有统一(指令/数据)L2缓存。所有缓存使用64字节的缓存行大小。

- 每个核心支持同时多线程(SMT),允许2个独立的硬件线程独立运行,并共享对应核心的L2缓存。

5、Core Complex (CCX)

下图显示了一个核心复合体(CCX),其中高达八个基于“Zen 4”的核心共享一个L3或最后一级缓存(LLC)。启用同时多线程(SMT)允许单个CCX支持高达16个并发硬件线程。

6、Core Complex Dies (CCDs)

如下图所示在AMD EPYC 9xx4系列处理器中,核心复合体芯片(CCD)可能包含一个或两个CCX,具体取决于处理器(91xx-96xx“Genoa” vs. 97xx“Bergamo”)。

在97xx型号的AMD EPYC 9004系列处理器中,每个核心复合体芯片(CCD)包含两个CCX。

| AMD EPYC 9004 Series Processor | 91xx-96xxq | 97xx |

|---|---|---|

| # of CCXs within a CCD | 1 | 2 |

可以使用以下一种或两种方法在BIOS中禁用核心:

- 将每个L3缓存中的核心数从8减少到7、6、5、4、3、2或1,同时保持CCD数量不变。此方法增加了每个核心的有效缓存比率,但减少了共享缓存的核心数量。

- 减少活动CCD的数量,同时保持每个CCD中的核心数不变。此方法保持了核心之间的缓存共享优势,同时保持了相同的每个核心的缓存比率。

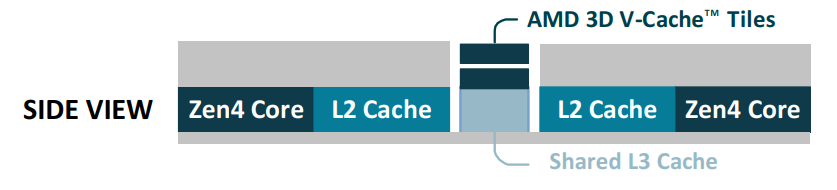

7、AMD 3D V-Cache™ Technology

AMD EPYC 9xx4X系列处理器采用了AMD 3D V-Cache™堆叠技术,实现了更高效的芯片集成。AMD 3D芯片组架构将L3缓存瓦片垂直堆叠,每个芯片提供高达96MB的L3缓存(每个插槽高达1GB的L3缓存),同时仍然与所有AMD EPYC™ 9004系列处理器型号保持插座兼容性。搭载AMD 3D V-Cache技术的AMD EPYC 9004系列处理器采用了业界领先的基于铜对铜混合键合的“无颗粒”芯片-晶圆堆叠工艺,实现了超过当前2D技术的200倍的互连密度(以及超过其他使用焊料凸点的3D技术的15倍以上的互连密度),从而实现了更低的延迟、更高的带宽以及更高的功率和热效率。

对于任何给定的部件,所有CCX始终包含相同数量的核心。然而,不同的OPNs可能具有不同数量的核心,但是对于同一型号的处理器,所有CCX始终包含相同数量的核心。

| AMD EPYC 9004 Series Processors | 9xx4 | 9004X OPNs (with 3D V-Cache) |

|---|---|---|

| Max Shared L3 Cache (per CCD) | 32 MB | 96 MB |

8、I/O Die (Infinity Fabric™)

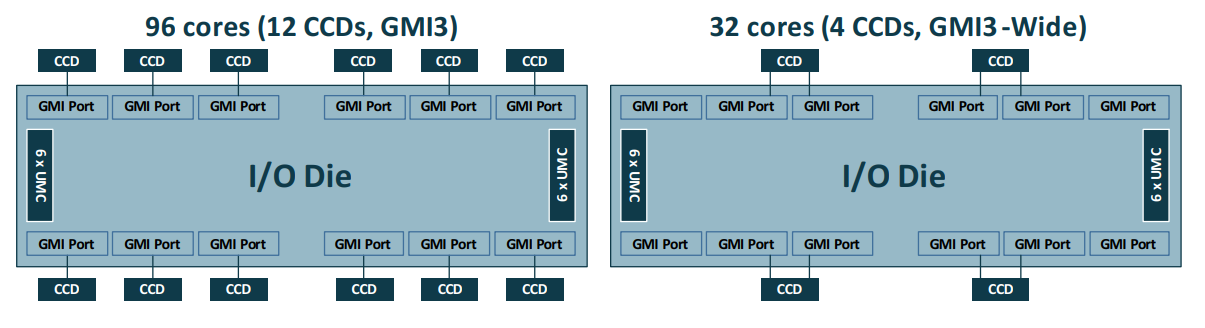

CCD通过更新的I/O芯片(IOD)连接到内存、I/O以及彼此。这个中央的AMD Infinity Fabric™提供了数据路径和控制支持,用于连接CCX、内存和I/O。每个CCD通过专用的高速全局内存互连(GMI)链路连接到IOD。IOD有助于维持缓存一致性,并通过其xGMI或G-链接提供接口,将数据传输到潜在的第二个处理器。AMD EPYC 9004系列处理器支持高达4个xGMI(或G-链接),速度高达32Gbps。IOD暴露了DDR5内存通道、PCIe® Gen5、CXL 1.1+和Infinity Fabric链路。所有芯片(芯片组)通过AMD Infinity Fabric技术相互连接。下图显示了一个96核的AMD EPYC 9654处理器的布局。AMD EPYC 9654有12个CCD,每个CCD通过自己的GMI连接到IOD。

AMD还提供“Wide”类型的OPN(例如AMD EPYC 9334),其中每个CCD连接到两个GMI3接口,从而使核心到I/O芯片的带宽加倍。IOD提供了十二个统一的内存控制器,支持DDR5内存。IOD还提供了4个“P-链接”,系统OEM/设计者可以配置以支持各种I/O接口,例如PCIe Gen5和/或CXL 1.1+。

9、Memory and I/O

每个UMC可以支持每通道最多2个DIMM(DPC),每个插槽最多可支持24个DIMM。OEM服务器配置可以允许每通道1个DIMM或每通道2个DIMM。第四代AMD EPYC处理器最多支持6TB的DDR5内存。与之前一代的AMD EPYC处理器相比,具有更多和更快的内存通道可以为高核心计数处理器提供额外的内存带宽。在2、4、6、8、10和12个通道上进行内存交错有助于优化各种工作负载和内存配置。每个处理器可以有一组4个P链接和4个G链接。OEM主板设计可以使用G链接连接到第二个第四代AMD EPYC处理器,或提供额外的PCIe Gen5通道。第四代AMD EPYC处理器支持高达八组x16位I/O通道,即在单插槽平台上支持128条高速PCIe Gen5通道,在双插槽平台上最多支持160条通道。此外,OEM可以将这128条通道中的32条配置为SATA通道和/或将64条通道配置为CXL 1.1+。总之,这些通道可以支持:

- 最多支持4个AMD Infinity Fabric连接的G-链接,适用于双插槽(2P)设计。

- 单插槽设计中,最多支持8个x16位或128条PCIe Gen 5连接,用于外围设备(在双插槽设计中最多支持160条通道)。

- 最多支持64条通道(4个P链接),可以用于专用于计算表达链接(CXL)1.1+连接到扩展内存。

- 最多支持32条I/O通道,可以配置为SATA磁盘控制器。

10、Visualizing AMD EPYC 9004 Series Processors (Family 19h)

10.1、Models 91xx-96xx (“Genoa”)

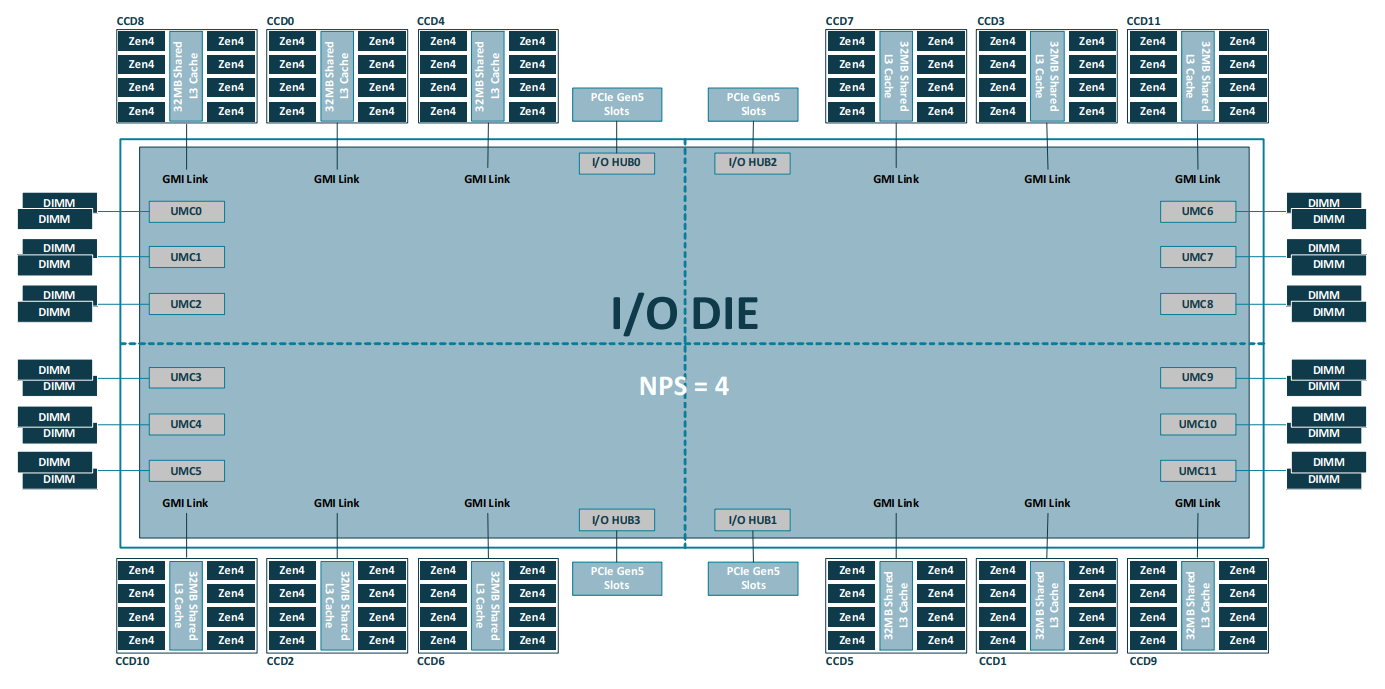

第四代AMD EPYC 9004处理器,型号为91xx-96xx,每个处理器最多有12个CCD,每个CCD包含一个单独的CCX,如下图所示。

10.2、Models 97xx (“Bergamo”)

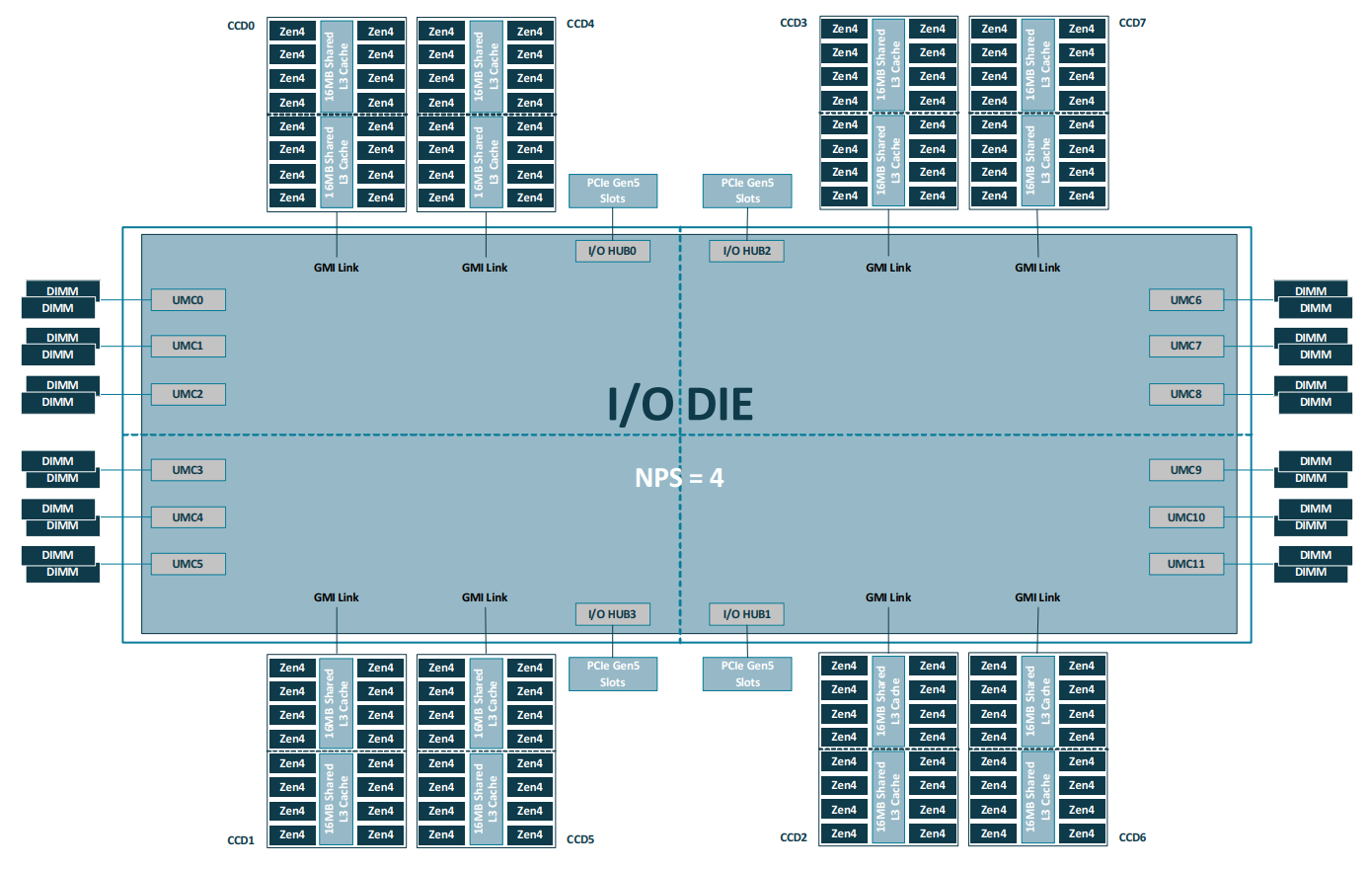

第四代AMD EPYC 9004系列处理器,型号为97xx,每个处理器最多有8个CCD,每个CCD包含两个CCX,如下图所示。

11、NUMA Topology

AMD EPYC 9004系列处理器采用非统一内存访问(NUMA)架构,其中处理器核心与内存和I/O控制器的接近程度可能导致不同的延迟。在同一NUMA节点中使用资源可提供统一良好的性能,而在不同节点中使用资源则会增加延迟。

用户可以调整系统的NUMA节点每插槽(NPS)BIOS设置,以优化其特定的操作环境和工作负载的NUMA拓扑结构。例如,将NPS设置为4,将处理器分成四个象限,每个象限有3个CCD、3个UMC和1个I/O中心。处理器-内存I/O之间最近的距离是在同一象限内核心、内存和I/O外设之间。最远的距离是在十字对角象限(或2P配置中的另一个处理器)内核心和内存控制器或I/O中心之间的距离。在基于NUMA的系统中,核心、内存和I/O中心/设备的局部性是调整性能的重要因素。

NPS设置还控制了NUMA节点内存通道的交错模式。在给定的NUMA节点内,每个内存通道都是交错的。随着NPS设置越来越精细,交错的通道数量会减少。例如:

当NPS设置为4时,将处理器分割成每个插槽四个NUMA节点,每个逻辑象限配置为自己的NUMA域。内存在与每个象限相关联的内存通道上交错。PCIe设备将位于四个处理器NUMA域中的一个,具体取决于IOD象限中是否有与该设备对应的PCIe根复杂结构。

当NPS设置为2时,将每个处理器配置为两个NUMA域,将一半的核心和一半的内存通道分为一个NUMA域,将其余的核心和内存通道分为第二个NUMA域。内存在每个NUMA域中的六个内存通道上交错。PCIe设备将位于两个NUMA节点中的一个,具体取决于具有该设备的PCIe根复杂结构的一半。

当NPS设置为1时,表示每个插槽一个单一的NUMA节点。此设置将处理器上的所有内存通道配置为一个单一的NUMA节点。所有处理器核心、所有连接的内存以及连接到SoC的所有PCIe设备都在该单个NUMA节点中。内存在处理器上的所有内存通道上交错成一个单一的地址空间。

当NPS设置为0时,表示整个系统的一个单一的NUMA域(在双插槽配置中跨两个插槽)。此设置将系统上的所有内存通道配置为一个单一的NUMA节点。内存在系统上的所有内存通道上交错成一个单一的地址空间。所有处理器核心跨所有插槽、所有连接的内存以及连接到任一处理器的所有PCIe设备都位于该单个NUMA域中。

在某些环境中,您还可以通过使用LLC(L3缓存)作为NUMA BIOS设置来进一步提高性能,将工作负载关联到共享单个LLC的计算核心。启用此设置将每个共享的L3或CCX等同于一个单独的NUMA节点,即每个CCD一个独特的L3缓存。当启用此设置时,单个AMD EPYC 9004系列处理器(具有12个CCD)最多可以有12个NUMA节点。因此,单个EPYC 9004系列处理器可以支持从每个插槽一个到十二个NUMA节点的各种NUMA配置。

[!NOTE]

注意:如果软件需要了解NUMA拓扑结构或核心枚举,必须使用文档化的操作系统(OS)API、明确定义的接口和命令。不要依赖过去关于APICID或CCX排序等设置的假设。

12、Dual-Socket Configurations

AMD EPYC 9004系列处理器支持单插槽或双插槽系统配置。在其名称中带有“P”后缀的处理器仅针对单插槽配置进行了优化。双插槽配置要求两个处理器必须完全相同。您不能在单个双插槽系统中使用两个不同的处理器订购部件号(OPNs)。双插槽系统总共有24个内存通道,每个插槽有12个。不同的OPN可以配置为支持各种NUMA域。

在双插槽系统中,通过它们各自的外部全局内存互连[xGMI]连接,将两个相同的EPYC 9004系列SoC连接在一起。这样就在两个处理器之间创建了一个高带宽、低延迟的互连。系统制造商可以根据I/O和带宽系统设计目标选择使用3个或4个这些Infinity Fabric连接。Infinity Fabric连接利用系统上的PCIe通道相同的物理连接。每个连接使用多达16个PCIe通道。典型的双插槽系统将每个插槽的64个PCIe通道(4个连接)重新配置为Infinity Fabric连接。这样每个插槽就有64个剩余的PCIe通道,这意味着系统总共有128个PCIe通道。在某些情况下,系统设计人员可能希望通过将Infinity Fabric G-Links的数量从4个减少到3个来为系统暴露更多的PCIe通道。在这些情况下,设计人员可以通过仅使用每个插槽的48个通道而不是64个通道来为PCIe分配多达160个通道(每个插槽80个)。

13、Processor Identification

软件使用CPUID指令(Fn0000_0001_EAX)来识别处理器,并返回以下值:

- Family: 19h 表示“Zen 4”架构

- Model: 与产品有关。例如,EPYC型号10h对应于“A”型号“Zen 4” CPU。

- 91xx-96xx(包括“X” OPNs): Family 19h 10-1F

- 97xx: Family 19h A0-AF

- Stepping: 可能用于进一步识别较小的设计更改

例如,Family、Model和Stepping(十进制)的CPUID值为25、17、1对应于“B1”型号“Zen 4” CPU。

14、Single-Socket Genoa CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR5 Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 5 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 9354P | 32 | 64 | 3.25 | 3.8 | 280 | 32 | 256 | 8 x CCD 1 x I/OD | 8 x 4 | 12 | 4800 | 460.8 | 128 |

| 9454P | 48 | 96 | 2.75 | 3.8 | 290 | 48 | 256 | 6 x CCD 1 x I/OD | 6 x 8 | 12 | 4800 | 460.8 | 128 |

| 9554P | 64 | 128 | 3.1 | 3.75 | 360 | 64 | 256 | 8 x CCD 1 x I/OD | 8 x 8 | 12 | 4800 | 460.8 | 128 |

| 9654P | 96 | 192 | 2.4 | 3.7 | 360 | 96 | 384 | 12x CCD 1 x I/OD | 12 x 8 | 12 | 4800 | 460.8 | 128 |

9654P / 9554P / 9454P : High Performance Computing

15、Dual socket CPUs

15.1、Genoa CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR5 Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 5 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 9124 | 16 | 32 | 3 | 3.7 | 200 | 16 | 64 | 2 x CCD 1 x I/OD | 2 x 8 | 12 | 4800 | 460.8 | 128 |

| 9224 | 24 | 48 | 2.5 | 3.7 | 200 | 24 | 64 | 3 x CCD 1 x I/OD | 3 x 8 | 12 | 4800 | 460.8 | 128 |

| 9254 | 24 | 48 | 2.9 | 4.15 | 200 | 24 | 128 | 4 x CCD 1 x I/OD | 4 x 6 | 12 | 4800 | 460.8 | 128 |

| 9334 | 32 | 64 | 2.7 | 3.9 | 210 | 32 | 128 | 4 x CCD 1 x I/OD | 4 x 8 | 12 | 4800 | 460.8 | 128 |

| 9354 | 32 | 64 | 3.25 | 3.8 | 280 | 32 | 256 | 8 x CCD 1 x I/OD | 8 x 4 | 12 | 4800 | 460.8 | 128 |

| 9454 | 48 | 96 | 2.75 | 3.8 | 290 | 48 | 256 | 6 x CCD 1 x I/OD | 6 x 8 | 12 | 4800 | 460.8 | 128 |

| 9534 | 64 | 128 | 2.45 | 3.7 | 280 | 64 | 256 | 8 x CCD 1 x I/OD | 8 x 8 | 12 | 4800 | 460.8 | 128 |

| 9554 | 64 | 128 | 3.1 | 3.75 | 360 | 64 | 256 | 8 x CCD 1 x I/OD | 8 x 8 | 12 | 4800 | 460.8 | 128 |

| 9634 | 84 | 168 | 2.25 | 3.7 | 360 | 84 | 384 | 12x CCD 1 x I/OD | 12 x 7 | 12 | 4800 | 460.8 | 128 |

| 9654 | 96 | 192 | 2.4 | 3.7 | 360 | 96 | 384 | 12x CCD 1 x I/OD | 12 x 8 | 12 | 4800 | 460.8 | 128 |

- 9654 / 9634 / 9554 / 9534 /9454 : High Performance Computing

15.2、Genoa-F High-Frequency CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR5 Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 5 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 9174F | 16 | 32 | 4.1 | 4.4 | 320 | 16 | 256 | 8 x CCD 1 x I/OD | 8 x 2 | 12 | 4800 | 460.8 | 128 |

| 9274F | 24 | 48 | 4.05 | 4.3 | 320 | 24 | 256 | 8 x CCD 1 x I/OD | 8 x 3 | 12 | 4800 | 460.8 | 128 |

| 9374F | 32 | 64 | 3.85 | 4.3 | 320 | 32 | 256 | 8 x CCD 1 x I/OD | 8 x 4 | 12 | 4800 | 460.8 | 128 |

| 9474F | 48 | 96 | 3.6 | 4.1 | 360 | 48 | 256 | 8 x CCD 1 x I/OD | 8 x 6 | 12 | 4800 | 460.8 | 128 |

- Genoa-F CPUs are specifically optimized for per-core license costs. They offer the highest possible clock frequency with a smaller number of cores and thus high performance per core.

15.3、Genoa-X HPC CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR5 Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 5 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 9184X | 16 | 32 | 3.55 | 4.2 | 320 | 16 | 768 | 8 x CCD 1 x I/OD | 8 x 2 | 12 | 4800 | 460.8 | 128 |

| 9384X | 32 | 64 | 3.1 | 3.9 | 320 | 32 | 768 | 8 x CCD 1 x I/OD | 8 x 4 | 12 | 4800 | 460.8 | 128 |

| 9684X | 96 | 192 | 2.55 | 3.7 | 400 | 96 | 1152 | 12x CCD 1 x I/OD | 12 x 8 | 12 | 4800 | 460.8 | 128 |

- With the Genoa-X series processors, AMD offers models with an enlarged Level 3 cache (3D V-Cache). This brings advantages especially in the high-performance computing (HPC) application area. In addition to the 96-core 9684X processor for HPC, the models with fewer cores are specifically optimized for per-core licensing (16 core 9184X for Windows Server, 32 core 9384X for VMware).

- 9684X : High Performance Computing

15.4、Bergamo 128 core CPUs

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR5 Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 5 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 9734 | 112 | 224 | 2.2 | 3 | 340 | 112 | 256 | 8 x CCD 1 x I/OD | 8 x 14 | 12 | 4800 | 460.8 | 128 |

| 9754S | 128 | 128 | 2.25 | 3.1 | 360 | 128 | 256 | 8 x CCD 1 x I/OD | 8 x 16 | 12 | 4800 | 460.8 | 128 |

| 9754 | 128 | 256 | 2.25 | 3.1 | 360 | 128 | 256 | 8 x CCD 1 x I/OD | 8 x 16 | 12 | 4800 | 460.8 | 128 |

- Bergamo CPUs (Zen 4c) have CCDs with less L3 cache (2 MB L3 cache/core instead of up to 4 MB L3 cache/core on Zen 4), but in return have more cores/CCD.

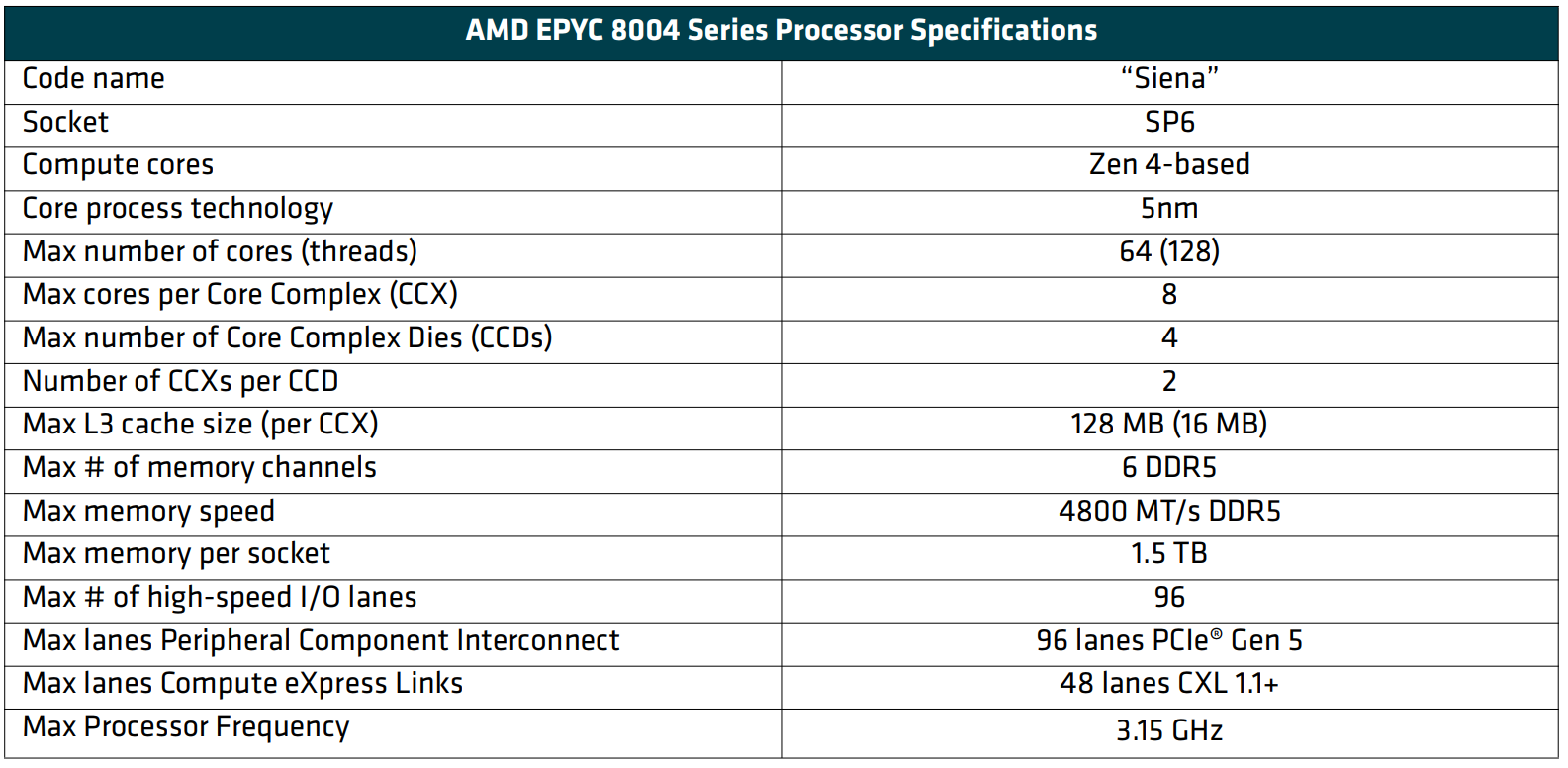

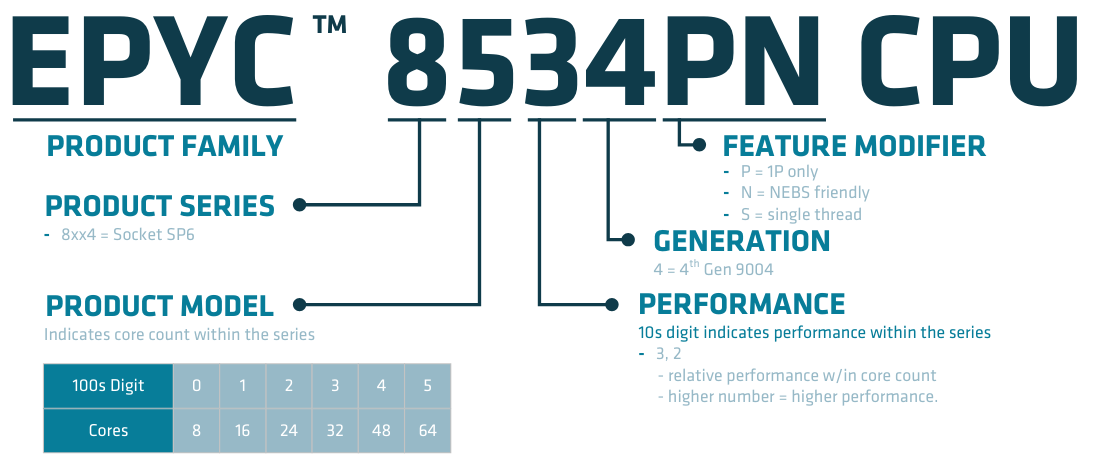

五、Siena Processors

1、General Specifications

第四代AMD EPYC 8004系列处理器提供了各种配置,包括不同数量的核心、热设计功耗(TDP)、频率、缓存大小等,这些配置进一步完善了AMD现有的服务器产品组合,并提高了性能、功耗效率和价值。下表列出了所有AMD EPYC 8004系列处理器共有的一些特点。

2、“Zen 4” Core

– 参考AMD EPYC™ 9004系列处理器介绍。

3、Core Complex (CCX)

– 参考AMD EPYC™ 9004系列处理器介绍。

4、Core Complex Dies (CCDs)

– 参考AMD EPYC™ 9004系列处理器介绍。

5、I/O Die (Infinity Fabric™)

CCD通过更新的I/O Die(IOD)连接到内存、I/O以及彼此。这个中央的AMD Infinity Fabric™提供了连接CCD、内存和I/O的数据路径和控制支持。每个CCD通过专用的高速全局内存互连(GMI)连接连接到IOD。IOD有助于维护缓存一致性。AMD EPYC 8004系列处理器支持高达32Gbps速度的最多4个xGMI(或G-Link)。IOD公开了DDR5内存通道、PCIe® Gen5、CXL 1.1+和Infinity Fabric连接。所有芯片(die)通过AMD Infinity Fabric技术相互连接。下图显示了64核AMD EPYC 8004处理器的布局。AMD EPYC 8004处理器最多有4个CCD,每个CCD通过自己的GMI连接连接到IOD。IOD提供了六个统一内存控制器,支持DDR5内存。IOD呈现了系统OEM/设计人员可以配置以支持各种IO接口的链接。

6、Memory and I/O

每个UMC最多可以支持2个DIMM每通道(DPC),最多可达12个DIMM。OEM服务器配置可以允许每个通道1个DIMM或2个DIMM。AMD EPYC 8004系列处理器支持高达3TB的DDR5内存。在2、3和6个通道上的内存交错有助于优化各种工作负载和内存配置。每个处理器有一组3个P-链接和3个G-链接。AMD EPYC 8004为OEM提供IO灵活性,使它们可以适当地优化其IO子系统。总共有6个x16或96个高速I/O通道。另外,还有8个PCIe Gen3的奖励通道可用。3个G-链接提供48条PCI Gen5支持通道。3个P-链接可以用于(48条通道)CXL 1.1+支持或(48条通道)PCI Gen5支持。或者,您可以使用32条通道用于SATA。

总结一下,这些链接可以支持:

- 最多6个x16位或96条通道的PCIe Gen 5连接到外设。

- 最多48条通道(3个P-链接)可以专用于连接到扩展内存的Compute Express Link(CXL)1.1+连接。

- 最多32个I/O通道可以配置为SATA磁盘控制器。

7、Visualizing AMD EPYC 8004 Series Processors

如下图所示,AMD EPYC 8004系列处理器最多有4个CCD,每个CCD包含两个CCX。注意:对于需要增加带宽的工作负载,AMD提供了Siena OPNs(例如AMD EPYC 8324),其中每个CCD通过两个GMI3接口连接到I/O Die。

8、NUMA Topology

AMD EPYC 8004系列处理器采用非均匀存储访问(NUMA)架构,处理器核心与内存和I/O控制器的距离不同,可能会导致不同的延迟。在同一NUMA节点内使用资源可以提供统一的良好性能,而在不同节点中使用资源会增加延迟。

用户可以调整系统的NUMA节点每个插槽(NPS)BIOS设置,以优化其特定的操作环境和工作负载的NUMA拓扑结构。例如,将NPS设置为2会将AMD EPYC处理器分为两半,每半部分有2个CCD、3个UMC和2个I/O Hub。处理器-内存-I/O之间最近的距离是在同一象限内的核心、内存和I/O外设之间。最远的距离是在不同的半部分之间的核心和内存控制器或IO集线器之间。在基于NUMA的系统中,核心、内存和IO集线器/设备的局部性是性能调优的重要因素。NPS设置还控制NUMA节点内存通道的交错模式。在给定的NUMA节点中,每个内存通道都会进行交错。随着NPS设置的细化,交错的通道数量会减少。例如:

- 将NPS设置为2会将处理器配置为两个NUMA域,将一半的核心和一半的内存通道分组到一个NUMA域中,将剩余的核心和内存通道分组到第二个NUMA域中。内存在每个NUMA域的三个内存通道之间进行交错。PCIe设备将位于两个NUMA节点中的一个,具体取决于具有该设备的PCIe根复杂性的一半。AMD建议大多数工作负载使用NPS1或NPS2。

- 将NPS设置为1表示单个NUMA节点。该设置将处理器上的所有内存通道配置为单个NUMA节点。所有处理器核心、所有连接的内存和所有连接到SoC的PCIe设备都位于一个NUMA节点中。内存在处理器上的所有内存通道之间进行交错,形成单个地址空间。

您还可以通过使用LLC(L3高速缓存)作为NUMA BIOS设置来进一步提高某些环境的性能,将工作负载关联到共享单个LLC的计算核心上。启用此设置将每个共享的L3或CCX等同于一个单独的NUMA节点,即每个CCD具有唯一的L3缓存。当启用此设置时,单个AMD EPYC 8004系列处理器可以具有最多8个NUMA节点,每个CCD一个。因此,单个EPYC 8004系列处理器可以支持从一个到四个NUMA节点的各种NUMA配置,具体取决于有多少个UMC被填充。在某些EPYC 8004系统/处理器上,NPS4可能是一个选项;然而,由于UMC的不对称性,通常情况下NPS1或NPS2会提供更好的结果。

[!NOTE]

注意:如果软件需要了解NUMA拓扑结构或核心枚举,必须使用文档化的操作系统(OS)API、明确定义的接口和命令。不要依赖过去关于APICID或CCX排序等设置的假设。

9、Processor Identification

软件使用CPUID指令(Fn0000_0001_EAX)来识别处理器,并返回以下值:

- Family:19h表示“Zen 4”架构

- Model:随产品而变化。例如,EPYC Model 10h对应于“Zen 4” CPU的“A”型部件。

- 8xx4:模型A0h–AFh

- Stepping:可用于进一步识别微小的设计更改

例如,Family、Model和Stepping(十进制)的CPUID值为25、17、1对应于“B1”型“Zen 4” CPU。

10、Siena CPU List

| Model | Cores | Threads | Base Freq. (GHz) | Max. Boost Freq. (GHz) | TDP (W) | L2 Cache (MB) | L3 Cache (MB) | Chiplets | Core Config | DDR5 Channels | Max DDR Freq. (1DPC) | Per-Socket Theoretical Memory (GB/s) | PCIe Gen 5 Lanes |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 8024P | 8 | 16 | 2.4 | 3.0 | 90 | 8 | 32 | 4 x CCD 1 x I/OD | 4 x 2 | 6 | 4800 | 230.4 | 96 |

| 8024PN | 8 | 16 | 2.05 | 3.0 | 80 | 8 | 32 | 4 x CCD 1 x I/OD | 4 x 2 | 6 | 4800 | 230.4 | 96 |

| 8124P | 16 | 32 | 2.45 | 3.0 | 125 | 16 | 64 | 4 x CCD 1 x I/OD | 4 x 4 | 6 | 4800 | 230.4 | 96 |

| 8124PN | 16 | 32 | 2.0 | 3.0 | 100 | 16 | 64 | 4 x CCD 1 x I/OD | 4 x 4 | 6 | 4800 | 230.4 | 96 |

| 8224P | 24 | 48 | 2.55 | 3.0 | 160 | 24 | 64 | 4 x CCD 1 x I/OD | 4 x 6 | 6 | 4800 | 230.4 | 96 |

| 8224PN | 24 | 48 | 2.0 | 3.0 | 120 | 24 | 64 | 4 x CCD 1 x I/OD | 4 x 6 | 6 | 4800 | 230.4 | 96 |

| 8324P | 32 | 64 | 2.65 | 3.0 | 180 | 32 | 128 | 4 x CCD 1 x I/OD | 4 x 8 | 6 | 4800 | 230.4 | 96 |

| 8324PN | 32 | 64 | 2.05 | 3.0 | 130 | 32 | 128 | 4 x CCD 1 x I/OD | 4 x 8 | 6 | 4800 | 230.4 | 96 |

| 8434P | 48 | 96 | 2.5 | 3.1 | 200 | 48 | 128 | 4 x CCD 1 x I/OD | 4 x 12 | 6 | 4800 | 230.4 | 96 |

| 8438PN | 48 | 96 | 2.0 | 3.0 | 155 | 48 | 128 | 4 x CCD 1 x I/OD | 4 x 12 | 6 | 4800 | 230.4 | 96 |

| 8534P | 64 | 128 | 2.3 | 3.1 | 200 | 64 | 128 | 4 x CCD 1 x I/OD | 4 x 16 | 6 | 4800 | 230.4 | 96 |

| 8534PN | 64 | 128 | 2.0 | 3.1 | 155 | 64 | 128 | 4 x CCD 1 x I/OD | 4 x 16 | 6 | 4800 | 230.4 | 96 |

- 8XX4PN : NEBS-FRIENDLY PROCESSORS

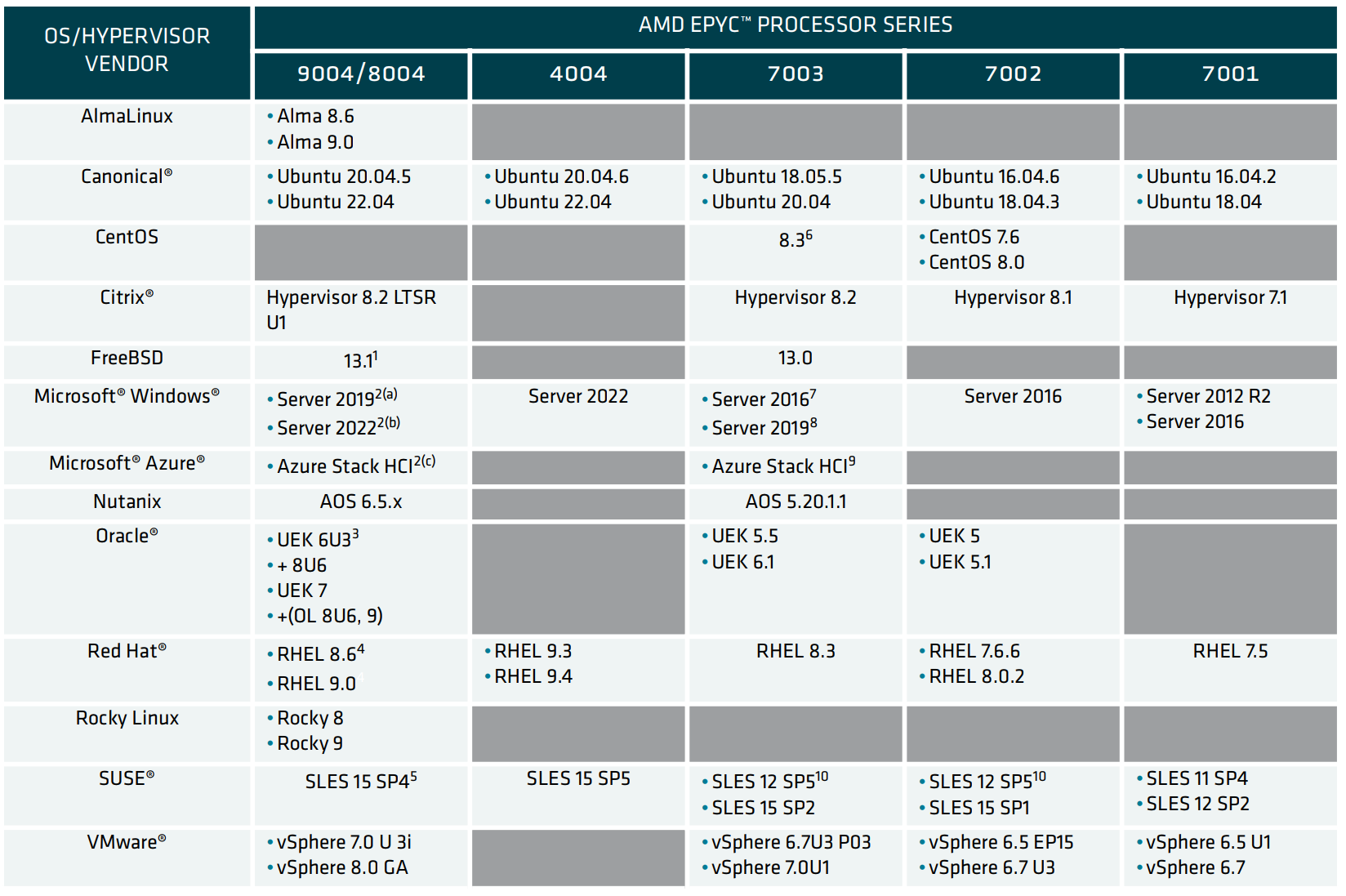

六、OS Support

Last Update: April 2024

FOOTNOTES:

- 1,Maximum 256T(1P or 2P with SMT disabled).

- 2,For 96c Genoa OPNs:

- (a) Windows Server 2019(WS’19) requires Windows Update 9C for bare-metal support (KB5017379). WS’19 Hyper-V support requires Windows Update 10B(KB5018419).

- (b) WS’22 requires Dec.21.iso or injecting KB5007254 patch into existing WS22.iso. WS’22 Hyper-V patch was released as Windows update 2C (KB5010421).

- (c) Azure Stack HCI 22H2/v3 GA’d on10/12/2022.

- 3,Plus August 26,2022 update:

- UEK 6U3 install on Oracle Linux 8.6 base

- UEK 7 install on Oracle Linux 8.6,9.0 base

- 4,Includes corresponding Alma and Rocky Linux versions. NOTE: CentOS is EOL.

- 5,SUSE Adaptable Linux Platform(ALP) is the next major version

- 6,CentOS 8 updates stop at end of 2021.

- 7,Does not support x2APIC(256 core).

- 8,x2APIC support starts with Server 2019 Sept.2019 media refresh.

- 9,Azure Stack HCI V1+.

- 10,Requires maintenance update(Mar 4, 2020). Kernel 4.12.14-144.17.

七、Summary

AMD EPYC处理器中最重要的创新是第二代EPYC处理器首次引入的混合多芯片架构。第二、第三和第四代AMD EPYC处理器将CPU核心和I/O功能的创新路径分解为两种不同类型的芯片,可以根据它们需要完成的任务在合适的时间轴上进行开发。例如,“Zen 4”核心采用5纳米技术生产,而I/O芯片则采用6纳米工艺制造。这比使用同一制造技术创建所有处理器功能更加灵活和动态。采用模块化方法,可以混合匹配CPU和I/O芯片,创建与工作负载要求密切匹配的专用处理器。这些处理器的核心数范围从高性能处理器(最多可达128个核心)到需要最少四个核心的小型系统处理器。由于具有小核心数的服务器需要的I/O资源较少,比拥有128个核心的服务器少得多,因此EPYC 4004系列具有相应缩减的I/O芯片,其功耗和带宽能力与核心数量相匹配。这种解耦使得在相同的热设计功耗范围内实现了更高的核心密度。每一代新产品都实现了双位数的性能增长,指令每周期的持续改进也在其中起到了作用。

在第四代AMD EPYC处理器中,AMD使用两种不同的核心来满足各种工作负载需求,通过变化核心的类型和数量以及包装方式。EPYC 9004系列采用SP5封装形式,该系列的处理器使用‘Zen 4’或‘Zen 4c’核心设计。EPYC 8004系列设计为较小的SP6封装,并优化用于单插槽环境,使用‘Zen 4c’核心。EPYC 4004系列使用AM5插槽,优化用于小型裸机服务器,使用‘Zen 4’核心和较小的I/O芯片。